Introduction

IC (Integrated Circuit) Design & Verification tools are specialized Electronic Design Automation (EDA) software used to design, simulate, verify, and prepare semiconductor chips for fabrication. These tools cover the full chip development lifecycle—from RTL design and synthesis to physical layout, timing analysis, and sign-off verification.

As modern chips grow increasingly complex—often containing billions of transistors—IC design tools have become essential for ensuring functionality, performance, and manufacturability. They are widely used in industries such as semiconductors, AI hardware, automotive electronics, telecommunications, and consumer devices.

Common use cases include:

- Designing digital and analog integrated circuits

- RTL simulation and functional verification

- Static timing and power analysis

- Physical design (placement and routing)

- Sign-off verification (DRC, LVS, reliability checks)

Key evaluation criteria:

- Simulation accuracy and verification depth

- Scalability for large SoC designs

- Support for HDL workflows (Verilog, VHDL, SystemVerilog)

- Integration across full IC design flow

- Performance and compute efficiency

- Ease of use and automation capabilities

- Ecosystem and foundry compatibility

- Support for advanced nodes and multi-die designs

- Licensing flexibility and cost

Best for: VLSI engineers, ASIC/SoC designers, verification engineers, semiconductor startups, and research labs.

Not ideal for: Beginners without hardware background or teams working on simple PCB or embedded projects.

Key Trends in IC Design & Verification Tools

- AI-driven chip design: Automation in synthesis, layout, and verification workflows

- Cloud-based EDA environments: Enabling distributed design teams and scalable compute

- Chiplet and multi-die design support: Managing modular architectures

- Advanced node support: Tools optimized for FinFET and beyond

- Verification automation: Increased use of UVM and coverage-driven methodologies

- Digital twin integration: Linking chip behavior with system-level simulation

- Open-source IC design movement: Tools like OpenROAD gaining traction

- Hardware security verification: Detecting vulnerabilities at RTL and gate level

- HPC acceleration: Distributed simulation and regression testing

- Unified design platforms: End-to-end workflows from RTL to sign-off

How We Selected These Tools (Methodology)

- Evaluated industry adoption across semiconductor companies

- Assessed coverage of full IC design flow

- Reviewed simulation and verification capabilities

- Analyzed performance for large-scale designs

- Considered integration with foundries and PDKs

- Evaluated ease of use and automation features

- Reviewed support and training ecosystem

- Included both commercial and open-source tools

- Considered digital, analog, and mixed-signal coverage

- Ensured relevance across multiple industries

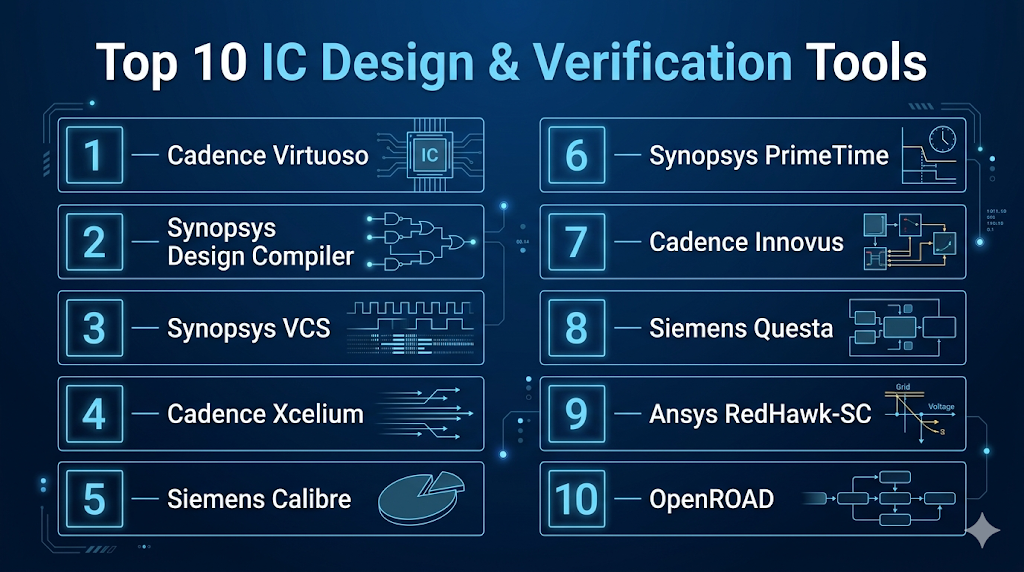

Top 10 IC Design & Verification Tools

#1 — Cadence Virtuoso

Short description: A leading platform for analog, mixed-signal, and custom IC design with deep verification capabilities.

Key Features

- Schematic-driven layout

- Advanced analog simulation

- Real-time design rule checking

- Multi-physics integration

- AI-assisted layout automation

- Foundry PDK support

Pros

- Industry-standard for analog design

- Highly accurate simulations

Cons

- Expensive

- Complex interface

Platforms / Deployment

- Windows / Linux

- Self-hosted / Cloud

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Deep integration with semiconductor workflows.

- Foundry PDKs

- Simulation tools

- APIs

- Verification suites

Support & Community

Strong enterprise support and widespread academic use.

#2 — Synopsys Design Compiler

Short description: A widely used logic synthesis tool for transforming RTL into gate-level designs.

Key Features

- RTL-to-gate synthesis

- Timing optimization

- Power optimization

- Constraint management

- Scalability for large designs

Pros

- High-quality synthesis results

- Widely adopted

Cons

- Expensive

- Requires expertise

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Core part of Synopsys ecosystem.

- Verification tools

- Timing analysis tools

- APIs

Support & Community

Strong enterprise documentation and support.

#3 — Synopsys VCS

Short description: A high-performance RTL simulation and verification tool for large-scale digital designs.

Key Features

- SystemVerilog simulation

- UVM-based verification

- Coverage-driven testing

- Debugging tools

- Scalable regression testing

Pros

- Excellent for large verification workloads

- Mature ecosystem

Cons

- Complex setup

- Expensive

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Strong integration with verification workflows.

- Debug tools

- APIs

- Automation scripts

Support & Community

Widely used in enterprise verification teams

#4 — Cadence Xcelium

Short description: A unified simulation platform for digital and mixed-signal verification.

Key Features

- High-speed simulation

- Mixed-language support

- Coverage analysis

- Debugging tools

- UVM support

Pros

- Strong performance

- Supports complex workflows

Cons

- Learning curve

- Licensing cost

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Works within Cadence ecosystem.

- Verification tools

- Simulation frameworks

- APIs

Support & Community

Strong enterprise support.

#5 — Siemens Calibre

Short description: A leading tool for physical verification and sign-off checks in IC design.

Key Features

- Design rule checking (DRC)

- Layout vs schematic (LVS)

- Parasitic extraction

- Reliability analysis

- Sign-off verification

Pros

- Industry-standard for sign-off

- Highly accurate

Cons

- Complex workflows

- Expensive

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Integrated with design flows.

- Foundry workflows

- CAD tools

- APIs

Support & Community

Strong enterprise adoption.

#6 — Synopsys PrimeTime

Short description: A widely used static timing analysis tool for validating chip performance.

Key Features

- Static timing analysis

- Power analysis

- Sign-off validation

- Multi-mode multi-corner analysis

- Advanced timing optimization

Pros

- Accurate timing analysis

- Industry standard

Cons

- Complex setup

- High cost

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Works across IC design flows.

- Synthesis tools

- Verification tools

- APIs

Support & Community

Strong enterprise support.

#7 — Cadence Innovus

Short description: A digital implementation platform for placement and routing in IC design.

Key Features

- Place and route (PnR)

- Timing optimization

- Power optimization

- Floorplanning tools

- Multi-core scalability

Pros

- Strong performance

- Scalable

Cons

- Complex workflows

- Requires expertise

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Part of Cadence ecosystem.

- Verification tools

- Timing tools

- APIs

Support & Community

Strong enterprise support.

#8 — Siemens Questa

Short description: A verification platform for simulation, formal verification, and debugging.

Key Features

- RTL simulation

- Formal verification

- Coverage analysis

- Debugging tools

- UVM support

Pros

- Strong verification capabilities

- Mature ecosystem

Cons

- Expensive

- Learning curve

Platforms / Deployment

- Windows / Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Supports verification workflows.

- Simulation tools

- APIs

- Debug tools

Support & Community

Strong enterprise usage.

#9 — Ansys RedHawk-SC

Short description: A power integrity and reliability analysis tool for advanced IC designs.

Key Features

- Power integrity analysis

- Thermal analysis

- Reliability modeling

- Electromigration analysis

- HPC support

Pros

- Strong reliability analysis

- Scalable

Cons

- Specialized use case

- Expensive

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Works with IC design flows.

- Simulation tools

- APIs

- HPC systems

Support & Community

Enterprise-level support.

#10 — OpenROAD

Short description: An open-source IC design automation platform for digital chip design workflows.

Key Features

- Automated RTL-to-GDS flow

- Placement and routing

- Timing optimization

- Open-source flexibility

- Integration with open toolchains

Pros

- Free and evolving

- Supports modern workflows

Cons

- Less mature

- Requires expertise

Platforms / Deployment

- Linux

- Self-hosted

Security & Compliance

- Not publicly stated

Integrations & Ecosystem

Works with open-source tools.

- APIs

- Simulation tools

- Custom workflows

Support & Community

Active developer community.

Comparison Table (Top 10)

| Tool Name | Best For | Platform(s) Supported | Deployment | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Cadence Virtuoso | Analog IC design | Windows, Linux | Hybrid | Schematic-driven layout | N/A |

| Synopsys Design Compiler | Synthesis | Linux | Self-hosted | RTL-to-gate conversion | N/A |

| Synopsys VCS | Verification | Linux | Self-hosted | High-speed simulation | N/A |

| Cadence Xcelium | Simulation | Linux | Self-hosted | Mixed-signal support | N/A |

| Siemens Calibre | Sign-off | Linux | Self-hosted | DRC/LVS accuracy | N/A |

| Synopsys PrimeTime | Timing | Linux | Self-hosted | Timing analysis | N/A |

| Cadence Innovus | Physical design | Linux | Self-hosted | Place & route | N/A |

| Siemens Questa | Verification | Windows, Linux | Self-hosted | Formal verification | N/A |

| Ansys RedHawk | Reliability | Linux | Self-hosted | Power integrity | N/A |

| OpenROAD | Open-source | Linux | Self-hosted | RTL-to-GDS automation | N/A |

Evaluation & Scoring of IC Design & Verification Tools

| Tool Name | Core (25%) | Ease (15%) | Integrations (15%) | Security (10%) | Performance (10%) | Support (10%) | Value (15%) | Weighted Total (0–10) |

|---|---|---|---|---|---|---|---|---|

| Virtuoso | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.3 |

| Design Compiler | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.3 |

| VCS | 9 | 6 | 9 | 7 | 9 | 9 | 6 | 8.2 |

| Xcelium | 9 | 6 | 8 | 7 | 9 | 8 | 6 | 8.0 |

| Calibre | 10 | 5 | 8 | 7 | 10 | 8 | 5 | 8.1 |

| PrimeTime | 9 | 5 | 8 | 7 | 9 | 8 | 5 | 7.8 |

| Innovus | 9 | 5 | 8 | 7 | 9 | 8 | 6 | 7.9 |

| Questa | 9 | 6 | 8 | 7 | 9 | 8 | 6 | 8.0 |

| RedHawk | 8 | 5 | 7 | 7 | 9 | 7 | 6 | 7.5 |

| OpenROAD | 7 | 4 | 6 | 5 | 7 | 6 | 10 | 6.8 |

How to interpret scores:

- Enterprise tools dominate in performance and core capabilities

- Verification tools are critical for large-scale chip design

- Open-source tools offer value but require expertise

- Ease of use is typically lower in advanced IC tools

- Always align tool choice with your design stage and complexity

Which IC Design & Verification Tool Is Right for You?

Solo / Freelancer

- Best options: OpenROAD

- Focus on cost and learning

SMB

- Best options: Mixed toolchains (OpenROAD + limited commercial tools)

- Balance cost and capability

Mid-Market

- Best options: Siemens Questa, Cadence Xcelium

- Strong verification workflows

Enterprise

- Best options: Cadence, Synopsys full suites

- End-to-end chip design

Budget vs Premium

- Budget: OpenROAD

- Premium: Cadence, Synopsys

Feature Depth vs Ease of Use

- Easy: Open-source tools

- Advanced: Cadence, Synopsys

Integrations & Scalability

- Strong: Synopsys, Cadence ecosystems

- Moderate: Open-source

Security & Compliance Needs

- Enterprise tools provide better governance

- Verification tools help ensure design correctness

Frequently Asked Questions (FAQs)

What are IC design tools used for?

They are used to design, simulate, and verify integrated circuits before manufacturing.

What is verification in IC design?

Verification ensures that the chip design behaves correctly under all conditions.

Are these tools expensive?

Yes, enterprise tools are costly, while open-source options are free.

What is RTL simulation?

It is the process of testing hardware designs written in HDL.

What is synthesis?

It converts RTL code into gate-level logic.

What is DRC and LVS?

They are checks to ensure designs meet manufacturing rules and match schematics.

Do I need coding skills?

Yes, knowledge of Verilog, VHDL, or SystemVerilog is essential.

Can beginners use these tools?

They are complex; beginners usually start with simplified tools.

What industries use IC tools?

Semiconductors, automotive, telecom, AI hardware, and consumer electronics.

Are open-source IC tools reliable?

They are improving but not yet equivalent to enterprise tools for large-scale designs.

Conclusion

IC Design & Verification tools form the backbone of modern semiconductor development, enabling engineers to design and validate complex chips with precision. From industry leaders like Cadence and Synopsys to emerging open-source platforms, the ecosystem offers a range of solutions tailored to different needs.